Link de descarga.

--------

Ejercicio N° 2: Para el siguiente circuito, verificar su funcionamiento, hallando mediante una tabla las condiciones de SET, RESET, ALMACENAMIENTO Y PROHIBIDA. Construir la tabla resumen.

Link de descarga.

---------

Ejercicio N° 3: ¿Qué es el clock ó reloj de los circuitos digitales? ¿Qué función cumple? ¿Qué es la frecuencia del clock y en que se mide?.

una señal de reloj es una señal usada para coordinar las acciones de dos o más circuitos digitales.

Una señal de reloj oscila entre estado alto o bajo, y gráficamente toma la forma de una onda cuadrada.La mayoría de los circuitos integrados complejos utilizan una señal de reloj para sincronizar sus diferentes partes y contar los tiempos de propagación. A medida que se fue incrementando la complejidad de los circuitos, se volvió más complicada la sincronización a través del reloj. Un ejemplo de circuito integrado complejo es el microprocesador. Bajo el término frecuencia de reloj se da a entender el ritmo con el que se tramitan los datos en un ordenador, y se especifica en herzios. Dado que la frecuencia de los procesadores modernos alcanza los miles de millones de herzios, las cantidades suelen representarse con la ayuda de prefijos como giga (G) para miles de millones y mega (M) para millones (mientras que para los sistemas embebidos aún es frecuente hablar de kHz). Por ejemplo, una frecuencia de reloj de 1 GHz significa un período de reloj de un nanosegundo. El flujo de datos de un procesador resulta de la frecuencia de reloj y del flujo de datos en su conexión con la memoria principal.

Ejercicio N° 4: Construir un Flip - Flop RS sincrónico, utilizando 4 compuertas NAND y obtener su tabla de funcionamiento a partir del flip - flop RS visto en el ejercicio N°1.

Link de descarga.

--------

Ejercicio N° 5: Los siguientes trenes de pulso se encuentran aplicados a los Flip - Flop RS sincronizado del ejercicio anterior. Dibujar las salidas Q y Q' correspondientes. El Flip - Flop se encuentra inicialmente en estado RESET.

Ejercicio Nº 7: Los siguientes trenes de pulso se encuentran aplicados a un Flip - Flop JK dibujar las salidas Q y Q'.

Ejercicio Nº 8: Construir un Flip - Flop JKMS utilizando 2 Flip - Flop JK.

Link de descarga.

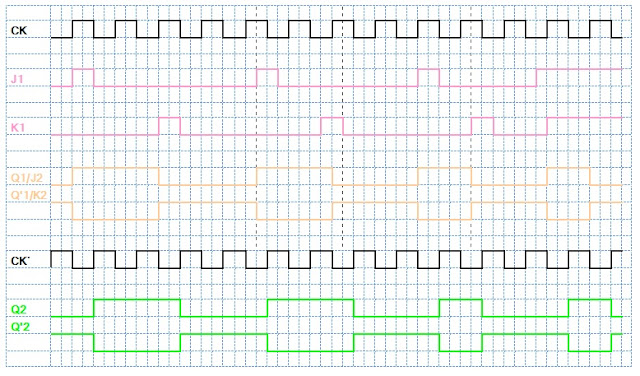

Ejercicio Nº 9: Para los siguientes trenes de pulso aplicados a un Flip - flop JKMS dibujar las salidas Q y Q'.

No hay comentarios:

Publicar un comentario